光制御FETOPTICALLY CONTROLLED FET

コンピュータの心臓部であるCPUは大規模集積回路からできていますが、その回路の大半はトランジスタ同士を結ぶ配線で占められています。しかしこの配線が長くなると信号の伝送時間が遅くなり、また消費電力も大きくなってしまいます。そこでこの配線を光で置き換えようという技術が提案されています。われわれはその一つの素子として光でトランジスタを動作させる"光制御FET"を提案、試作しています。これにより集積回路間の通信をチップ間の立体的な光通信にすることにより、「時間」「空間」軸を有効に使用しようと考えています。

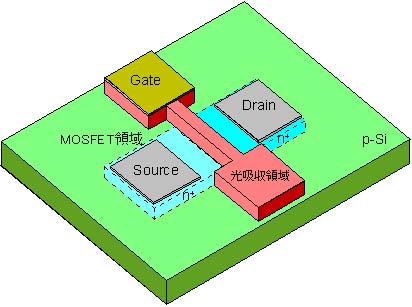

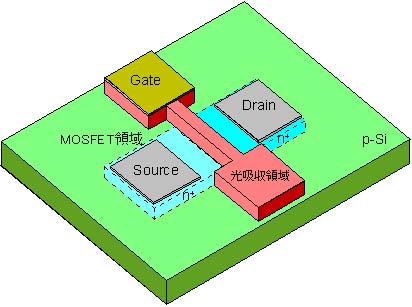

光制御FETは光を吸収する光吸収領域と電流を制御するFET領域が一体化された構造となっており、両者が直接貼付技術を用いて集積化されています。これまでFET領域はSi-MOSFET、GaAs/AlGaAs HEMT、GaAs MESFETを用い、光吸収領域は長波長帯の光を吸収するGaInAsバルクあるいはGaInAs/InP多重量子井戸構造を用いて試作し、その基本的な動作を確認しました。光制御MOSFETにおいては、ゲート長3.5μmの素子において、光-電気変換効率(応答感度)として最大1850A/Wを達成しました。

光制御FETは光を吸収する光吸収領域と電流を制御するFET領域が一体化された構造となっており、両者が直接貼付技術を用いて集積化されています。これまでFET領域はSi-MOSFET、GaAs/AlGaAs HEMT、GaAs MESFETを用い、光吸収領域は長波長帯の光を吸収するGaInAsバルクあるいはGaInAs/InP多重量子井戸構造を用いて試作し、その基本的な動作を確認しました。光制御MOSFETにおいては、ゲート長3.5μmの素子において、光-電気変換効率(応答感度)として最大1850A/Wを達成しました。

バナースペース

下村研究室

〒102-8554

東京都千代田区紀尾井町7-1

4号館275A室